How Micron Plans to Improve Its Gross Margin in Fiscal 2018

For fiscal 2Q18, Micron expects to improve its gross margin to 56.0% at the midpoint.

Jan. 22 2018, Updated 7:31 a.m. ET

Micron’s profitability

Earlier in this series, we saw that Micron Technology (MU) has been seeing increasing DRAM (dynamic random access memory) ASP (average selling price) for more than 18 months, which pushed its revenues up. The company also ramped up production on advanced manufacturing nodes, which reduced its cost per bit.

It also developed value-added products like GDDR5 (graphics double data rate) for NVIDIA (NVDA) and SSDs (solid-state drives) for PC OEMs,[1. original equipment manufacturers] which increased its sales volume. These factors drove the company’s gross margin.

Gross margin

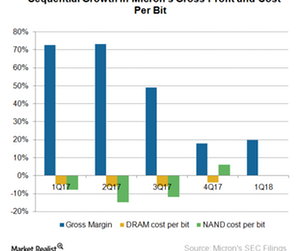

Micron’s non-GAAP[2. generally accepted accounting principles] gross margin more than doubled from 26.0% in fiscal 1Q17 to 55.0% in fiscal 1Q18. In dollar terms, Micron’s gross profit rose 265.0% YoY (year-over-year) and 19.8% sequentially to ~$3.8 billion in fiscal 1Q18.

The company stopped providing information about the cost per bit from fiscal 1Q18 onward. For fiscal 2Q18, Micron expects to improve its gross margin to 56.0% at the midpoint.

Gross profit is a product of ASP and cost per bit. As seen from the chart above, Micron’s gross profit rose 73.0% sequentially in fiscal 2Q17 as both DRAM and NAND cost per bit fell 6.0% and 15.0%, respectively. Its DRAM ASP rose 21.0% sequentially.

However, the cost per bit reduction slowed in fiscal 4Q17, slowing the gross profit growth to 18.0% sequentially.

As Micron moves to a smaller node, the cost-benefit ratio decreases as the technology becomes more complex. Moreover, a DRAM price increase is expected to moderate and NAND price is expected to fall in 2018.

As the cost-benefit ratio from technology slows and its ASP growth moderates, Micron is looking to reduce its cost and increase its gross profit by improving its manufacturing efficiency.

Micron’s efforts to boost manufacturing efficiency

Micron has hired Western Digital’s (WDC) silicon operations head, Manish Bhatia, to lead its global operations unit. He would be responsible for improving manufacturing and supply chain efficiencies. The company has already started cost optimization initiatives.

Micron manufactures 60.0% of its DRAM output in Taiwan (EWT). In order to improve its supply chain efficiency, it is ramping up assembly and testing capability at its new back-end facility in Taiwan and is looking to build a chip packaging factory in the country.

Hence, the DRAM produced in Taiwan would be assembled, tested, and packaged in Taiwan itself, thereby reducing costs.

Next, we’ll look at Micron’s operating margins.