Will Intel Continue to Benefit from Moore’s Law?

Intel’s (INTC) gross margin hasn’t improved much over the last two years because it’s been manufacturing chips on the same 14nm (nanometer) node since 2014.

Apr. 27 2017, Updated 9:08 a.m. ET

Moore’s law

Intel’s (INTC) gross margin hasn’t improved much over the last two years because it’s been manufacturing chips on the same 14nm (nanometer) node since 2014.

According to Moore’s law, the number of ICs (integrated circuit) per chip should double every two years with a shrink in the node, improving power efficiency and reducing costs.

Moore’s law slows

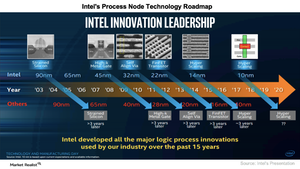

In the 2000s, it became difficult to double ICs simply by shrinking process nodes. Intel made several process innovations to keep Moore’s law alive. It invented techniques such as strained silicon, high-κ metal gates, self-aligned via, and FinFETs (fin field-effect transistors), which helped it to double its number of ICs with each shrink in the node in less than three years.

However, the recent process shrink to a 10nm (nanometer) node took longer than usual, forcing Intel to change its technology model from tick-tock (two processors for every node) to process, architecture, and optimization. The company launched three processors on the 14nm node: Broadwell in 2014, SkyLake in 2015, and KabyLake in 2016.

Although the company is set to launch its 10nm node in 2H17, it plans to launch a fourth processor called Coffee Lake on its 14nm node in 2017. Many analysts believe that Moore’s law is coming to an end. However, Intel says otherwise.

Moore’s law isn’t dead

At its Technology Manufacturing Day in March 2017, Intel’s Technology and Manufacturing Group director, Mark Bohr, explained that Moore’s law isn’t dead. Although the 10nm node took three years, it increased its transistor density 2.7x from 14nm.

Intel used the hyperscaling technique in its 10nm node. It reduced the dummy gates used to cover a logic cell from two to one, packing the cells more closely. It also stacked up contacts that connected gates to the metal layer of the chip, increasing the transistor density. This change helped Intel squeeze 100 million transistors into a 10nm node, compared to 37.5 million transistors in its 14nm node.

Intel’s process nodes continue to lead in terms of technology

Intel claims that its 14nm process is denser than TSMC’s (TSM) and Samsung’s (SSNLF) 16nm and 14nm process nodes. Samsung’s newly-launched 10nm node, on which Qualcomm (QCOM) has built its new Snapdragon 835, is similar to Intel’s 14nm node in terms of transistor density. When Intel’s 10nm node comes online in 2H17, it should once again gain a process lead over other foundries, according to Bohr.

According to Intel’s metrics, its 14nm process offers 37.5 MTr/mm2 (mega transistors per millimeter squared), whereas other 14nm and 16nm processes offer ~28 MTr/mm2. Intel’s 10nm process will offer 100.8MTr/mm2, whereas competing 10nm processes are expected to offer ~50MTr/mm2.

Intel is now bringing its process leadership to other companies by entering the foundry business. We’ll look into this in the next article.